Some contents are subject to change without notice.

#### **MITSUBISHI LSIs**

# MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

### DESCRIPTION

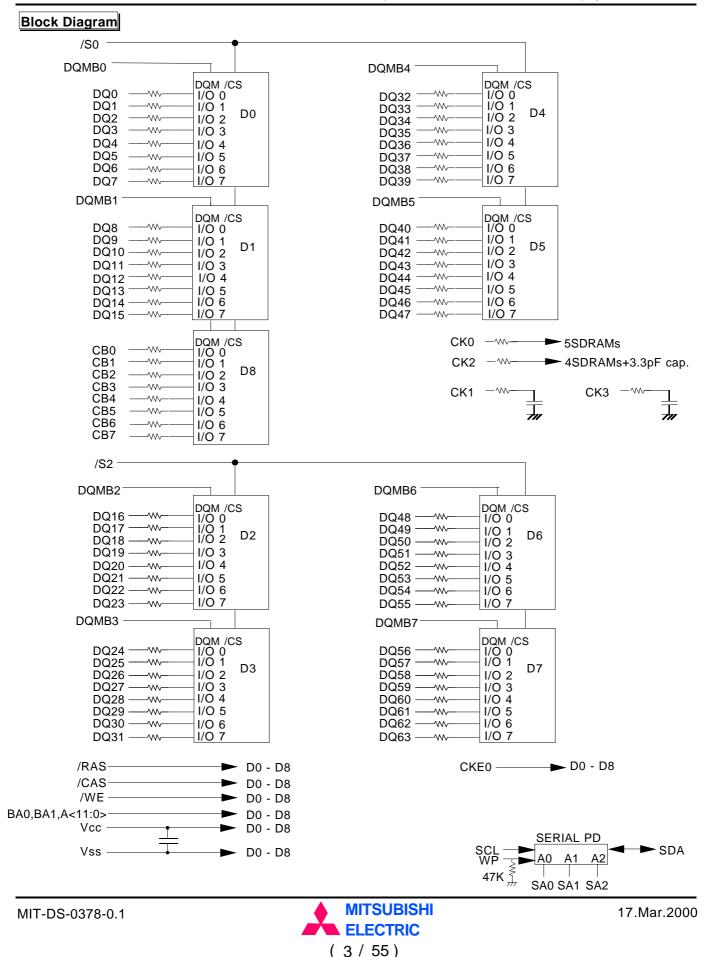

The MH16S72APHB is 16777216 - word by 72-bit Synchronous DRAM module. This consists of nine industry standard 16Mx8 Synchronous DRAMs in TSOP and one industory standard EEPROM in TSSOP.

The mounting of TSOP on a card edge Dual Inline package provides any application where high densities and large quantities of memory are required.

This is a socket type - memory modules, suitable for easy interchange or addition of modules.

#### FEATURES

|    | Frequency | CLK Access Time<br>(Component SDRAM) |

|----|-----------|--------------------------------------|

| -6 | 133MHz    | 5.4ns(CL=3)                          |

| -7 | 100MHz    | 6.0ns(CL=2)                          |

| -8 | 100MHz    | 6.0ns(CL=3)                          |

- Utilizes industry standard 16M x 8 Synchronous DRAMs TSOP and industry standard EEPROM in TSSOP

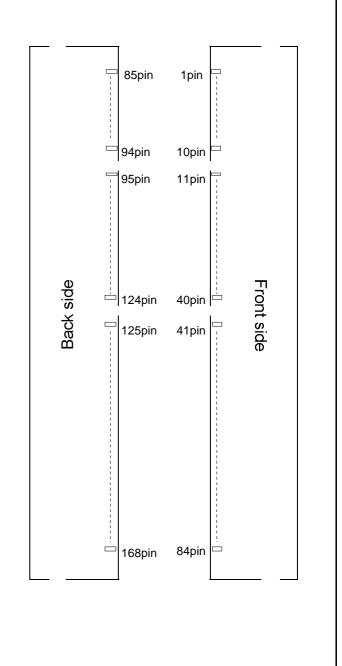

- 168-pin (84-pin dual in-line package)

- single 3.3V±0.3V power supply

- Max. Clock frequency -6:133MHz,-7,8:100MHz

- Fully synchronous operation referenced to clock rising edge

- 4 bank operation controlled by BA0,1(Bank Address)

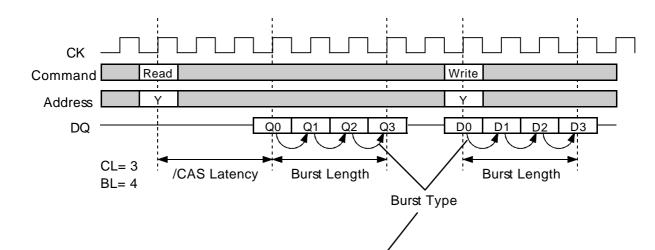

- /CAS latency- 2/3(programmable)

- Burst length- 1/2/4/8/Full Page(programmable)

- Burst type- sequential / interleave(programmable)

- Column access random

- Auto precharge / All bank precharge controlled by A10

- Auto refresh and Self refresh

- 4096 refresh cycle /64ms

- LVTTL Interface

- Discrete IC and module design conform to PC100/PC133 specification.

APPLICATION

PC main memory

MIT-DS-0378-0.1

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

| PIN NO. | PIN NAME |

|---------|----------|---------|----------|---------|----------|---------|----------|

| 1       | VSS      | 43      | VSS      | 85      | VSS      | 127     | VSS      |

| 2       | DQ0      | 44      | NC       | 86      | DQ32     | 128     | CKE0     |

| 3       | DQ1      | 45      | /S2      | 87      | DQ33     | 129     | NC       |

| 4       | DQ2      | 46      | DQMB2    | 88      | DQ34     | 130     | DQMB6    |

| 5       | DQ3      | 47      | DQMB3    | 89      | DQ35     | 131     | DQMB7    |

| 6       | VDD      | 48      | NC       | 90      | VDD      | 132     | NC       |

| 7       | DQ4      | 49      | VDD      | 91      | DQ36     | 133     | VDD      |

| 8       | DQ5      | 50      | NC       | 92      | DQ37     | 134     | NC       |

| 9       | DQ6      | 51      | NC       | 93      | DQ38     | 135     | NC       |

| 10      | DQ7      | 52      | CB2      | 94      | DQ39     | 136     | CB6      |

| 11      | DQ8      | 53      | CB3      | 95      | DQ40     | 137     | CB7      |

| 12      | VSS      | 54      | VSS      | 96      | VSS      | 138     | VSS      |

| 13      | DQ9      | 55      | DQ16     | 97      | DQ41     | 139     | DQ48     |

| 14      | DQ10     | 56      | DQ17     | 98      | DQ42     | 140     | DQ49     |

| 15      | DQ11     | 57      | DQ18     | 99      | DQ43     | 141     | DQ50     |

| 16      | DQ12     | 58      | DQ19     | 100     | DQ44     | 142     | DQ51     |

| 17      | DQ13     | 59      | VDD      | 101     | DQ45     | 143     | VDD      |

| 18      | VDD      | 60      | DQ20     | 102     | VDD      | 144     | DQ52     |

| 19      | DQ14     | 61      | NC       | 103     | DQ46     | 145     | NC       |

| 20      | DQ15     | 62      | NC       | 104     | DQ47     | 146     | NC       |

| 21      | CB0      | 63      | NC       | 105     | CB4      | 147     | NC       |

| 22      | CB1      | 64      | VSS      | 106     | CB5      | 148     | VSS      |

| 23      | VSS      | 65      | DQ21     | 107     | VSS      | 149     | DQ53     |

| 24      | NC       | 66      | DQ22     | 108     | NC       | 150     | DQ54     |

| 25      | NC       | 67      | DQ23     | 109     | NC       | 151     | DQ55     |

| 26      | VDD      | 68      | VSS      | 110     | VDD      | 152     | VSS      |

| 27      | /WE0     | 69      | DQ24     | 111     | /CAS     | 153     | DQ56     |

| 28      | DQMB0    | 70      | DQ25     | 112     | DQMB4    | 154     | DQ57     |

| 29      | DQMB1    | 71      | DQ26     | 113     | DQMB5    | 155     | DQ58     |

| 30      | /S0      | 72      | DQ27     | 114     | NC       | 156     | DQ59     |

| 31      | NC       | 73      | VDD      | 115     | /RAS     | 157     | VDD      |

| 32      | VSS      | 74      | DQ28     | 116     | VSS      | 158     | DQ60     |

| 33      | A0       | 75      | DQ29     | 117     | A1       | 159     | DQ61     |

| 34      | A2       | 76      | DQ30     | 118     | A3       | 160     | DQ62     |

| 35      | A4       | 77      | DQ31     | 119     | A5       | 161     | DQ63     |

| 36      | A6       | 78      | VSS      | 120     | A7       | 162     | VSS      |

| 37      | A8       | 79      | CK2      | 121     | A9       | 163     | CK3      |

| 38      | A10      | 80      | NC       | 122     | BA0      | 164     | NC       |

| 39      | BA1      | 81      | WP       | 123     | A11      | 165     | SA0      |

| 40      | VDD      | 82      | SDA      | 124     | VDD      | 166     | SA1      |

| 41      | VDD      | 83      | SCL      | 125     | CK1      | 167     | SA2      |

| 42      | CK0      | 84      | VDD      | 126     | NC       | 168     | VDD      |

NC = No Connection

Some contents are subject to change without notice.

#### **MITSUBISHI LSIs**

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

Some contents are subject to change without notice.

**MITSUBISHI LSIs**

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

## Serial Presence Detect Table I

| Byte | Function described                                      |         | SPD enrty data               | SPD DATA(hex) |

|------|---------------------------------------------------------|---------|------------------------------|---------------|

| 0    | Defines # bytes written into serial memory at module mf | far     | 128                          | 80            |

| 1    | Total # bytes of SPD memory device                      | -       | 256 Bytes                    | 08            |

| 2    | Fundamental memory type                                 |         | SDRAM                        | 04            |

| 3    | # Row Addresses on this assembly                        |         | A0-A11                       | 0C            |

| 4    | # Column Addresses on this assembly                     |         | A0-A9                        | 0A            |

| 5    | # Module Banks on this assembly                         |         | 1BANK                        | 01            |

| 6    | Data Width of this assembly                             |         | x72                          | 48            |

| 7    | Data Width continuation                                 |         | 0                            | 00            |

| 8    | Voltage interface standard of this assembly             |         | LVTTL                        | 01            |

| 9    | SDRAM Cycletime at Max. Supported CAS Latency (CL).     | -6      | 7.5ns                        | 75            |

|      | Cycle time for CL=3                                     | -7,-8   | 10ns                         | AO            |

| 10   | SDRAM Access from Clock                                 | -6      | 5.4ns                        | 54            |

|      | tAC for CL=3                                            | -7,-8   | 6ns                          | 60            |

| 11   | DIMM Configuration type (Non-parity,Parity,ECC)         |         | ECC                          | 02            |

| 12   | Refresh Rate/Type                                       |         | self refresh(15.625uS)       | 80            |

| 13   | SDRAM width, Primary DRAM                               |         | x8                           | 08            |

| 14   | Error Checking SDRAM data width                         |         | x8                           | 08            |

| 15   | Minimum Clock Delay,Back to Back Random Column Add      | dresses | 1                            | 01            |

| 16   | Burst Lengths Supported                                 |         | 1/2/4/8/Full page            | 8F            |

| 17   | # Banks on Each SDRAM device                            |         | 4bank                        | 04            |

| 18   | CAS# Latency                                            |         | 2/3                          | 06            |

| 19   | CS# Latency                                             |         | 0                            | 01            |

| 20   | Write Latency                                           |         | 0                            | 01            |

| 21   | SDRAM Module Attributes                                 |         | non-buffered,non-registered  | 00            |

| 22   | SDRAM Device Attributes:General                         |         | Precharge All,Auto precharge | 0E            |

| 23   | SDRAM Cycle time(2nd highest CAS latency)               | -6      | 10ns                         | AO            |

|      | Cycle time for CL=2                                     | -7      | 10ns                         | AO            |

|      |                                                         | -8      | 13ns                         | D0            |

| 24   | SDRAM Access form Clock(2nd highest CAS latency)        | -6      | 6ns                          | 60            |

|      | tAC for CL=2                                            | -7      | 6ns                          | 60            |

|      |                                                         | -8      | 7ns                          | 70            |

| 25   | SDRAM Cycle time(3rd highest CAS latency)               |         | N/A                          | 00            |

| 26   | SDRAM Access form Clock(3rd highest CAS latency)        |         | N/A                          | 00            |

| 27   | Precharge to Active Minimum                             | -6      | 22.5ns                       | 17            |

|      |                                                         | -7,-8   | 20ns                         | 14            |

| 28   | Row Active to Row Active Min.                           | -6      | 15ns                         | 0F            |

|      |                                                         | -7,-8   | 20ns                         | 14            |

| 29   | RAS to CAS Delay Min                                    | -6      | 22.5ns                       | 17            |

|      |                                                         | -7,-8   | 20ns                         | 14            |

| 30   | Active to Precharge Min                                 | -6      | 45ns                         | 2D            |

|      |                                                         | -7,-8   | 50ns                         | 32            |

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

# Serial Presence Detect Table II

| 31     | Density of each bank on module               |       | 128MByte         | 20                                   |

|--------|----------------------------------------------|-------|------------------|--------------------------------------|

| 32     | Command and Address signal input setup time  | -6    | 1.5ns            | 15                                   |

|        |                                              | -7,-8 | 2ns              | 20                                   |

| 33     | Command and Address signal input hold time   | -6    | 0.8ns            | 08                                   |

|        |                                              | -7,-8 | 1ns              | 10                                   |

| 34     | Data signal input setup time                 | -6    | 1.5ns            | 15                                   |

|        |                                              | -7,-8 | 2ns              | 20                                   |

| 35     | Data signal input hold time                  | -6    | 0.8ns            | 08                                   |

|        |                                              | -7,-8 | 1ns              | 10                                   |

| 36-61  | Superset Information (may be used in future) |       | option           | 00                                   |

| 62     | SPD Revision                                 |       | rev 1.2B         | 12                                   |

| 63     | Checksum for bytes 0-62                      |       | Check sum for -6 | C7                                   |

|        |                                              |       | Check sum for -7 | 28                                   |

|        |                                              |       | Check sum for -8 | 68                                   |

| 64-71  | Manufactures Jedec ID code per JEP-108E      |       | MITSUBISHI       | 1CFFFFFFFFFFFFF                      |

| 72     | Manufacturing location                       |       | Miyoshi,Japan    | 01                                   |

|        |                                              |       | Tajima,Japan     | 02                                   |

|        |                                              |       | NC,USA           | 03                                   |

|        |                                              |       | Germany          | 04                                   |

|        |                                              | _     | MH16S72APHB-6    | 4D483136533732415048422D362020202020 |

| 73-90  | Manufactures Part Number                     |       | MH16S72APHB-7    | 4D483136533732415048422D372020202020 |

|        |                                              |       | MH16S72APHB-8    | 4D483136533732415048422D382020202020 |

| 91-92  | Revision Code                                |       | PCB revision     | rrrr                                 |

| 93-94  | Manufacturing date                           |       | year/week code   | уумм                                 |

| 95-98  | Assembly Serial Number                       |       | serial number    | SSSSSSS                              |

| 99-125 | Manufacture Specific Data                    |       | option           | 00                                   |

| 126    | Intetl specification frequency               |       | 100MHz           | 64                                   |

| 127    | Intel specification CAS# Latency support     | -6,-7 | CL=2/3,AP,CK0,2  | AF                                   |

|        |                                              | -8    | CL=3,AP,CK0,2    | AD                                   |

| 128+   | Unused storage locations                     | T     | open             | 00                                   |

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

# **PIN FUNCTION**

| CK<br>(CK0 ~ CK3) | Input        | Master Clock:All other inputs are referenced to the rising edge of CK                                                                                                                                                                                                                                                                                 |

|-------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CKE0              | Input        | Clock Enable:CKE controls internal clock.When CKE is<br>low,internal clock for the following cycle is ceased. CKE is<br>also used to select auto / self refresh. After self refresh<br>mode is started, CKE becomes asynchronous input.Self<br>refresh is maintained as long as CKE is low.                                                           |

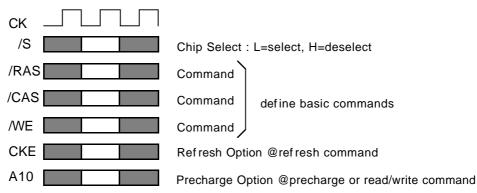

| /S<br>(/S0,2)     | Input        | Chip Select: When /S is high,any command means<br>No Operation.                                                                                                                                                                                                                                                                                       |

| /RAS,/CAS,/WE     | Input        | Combination of /RAS,/CAS,/WE defines basic commands.                                                                                                                                                                                                                                                                                                  |

| A0-11             | Input        | A0-11 specify the Row/Column Address in conjunction with<br>BA.The Row Address is specified by A0-11.The Column<br>Address is specified by A0-9.A10 is also used to indicate<br>precharge option.When A10 is high at a read / write<br>command, an auto precharge is performed. When A10 is<br>high at a precharge command, all banks are precharged. |

| BA0,1             | Input        | Bank Address:BA0,1 is not simply BA.BA specifies the<br>bank to which a command is applied.BA0,1 must be set<br>with ACT,PRE,READ,WRITE commands                                                                                                                                                                                                      |

| DQ0-63<br>CB0-7   | Input/Output | Data In and Data out are referenced to the rising edge of CK                                                                                                                                                                                                                                                                                          |

| DQMB0-7           | Input        | Din Mask/Output Disable:When DQMB is high in burst<br>write.Din for the current cycle is masked.When DQMB is<br>high in burst read,Dout is disabled at the next but one cycle.                                                                                                                                                                        |

| Vdd,Vss           | Power Supply | Power Supply for the memory mounted module.                                                                                                                                                                                                                                                                                                           |

| SCL               | Input        | Serial clock for serial PD                                                                                                                                                                                                                                                                                                                            |

| SDA               | Output       | Serial data for serial PD                                                                                                                                                                                                                                                                                                                             |

| SA0-3             | Input        | Address input for serial PD                                                                                                                                                                                                                                                                                                                           |

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

# **BASIC FUNCTIONS**

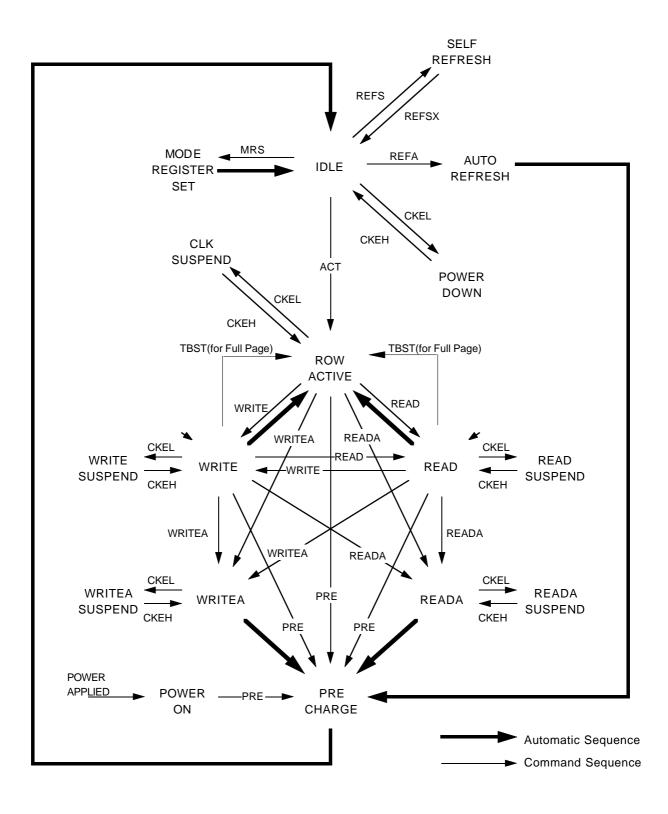

The MH16S72APHB provides basic functions, bank(row)activate, burst read / write, bank(row)precharge, and auto / self refresh.

Each command is defined by control signals of /RAS,/CAS and /WE at CK rising edge. In addition to 3 signals,/S,CKE and A10 are used as chip select,refresh option,and precharge option,respectively.

To know the detailed definition of commands please see the command truth table.

## Activate(ACT) [/RAS =L, /CAS = /WE =H]

ACT command activates a row in an idle bank indicated by BA.

## Read(READ) [/RAS =H,/CAS =L, /WE =H]

READ command starts burst read from the active bank indicated by BA.First output data appears after /CAS latency. When A10 =H at this command, the bank is deactivated after the burst read(auto-precharge, **READA**).

## Write(WRITE) [/RAS =H, /CAS = /WE =L]

WRITE command starts burst write to the active bank indicated by BA. Total data length to be written is set by burst length. When A10 =H at this command, the bank is deactivated after the burst write(auto-precharge,**WRITEA**).

## Precharge(PRE) [/RAS =L, /CAS =H,/WE =L]

PRE command deactivates the active bank indicated by BA. This command also terminates burst read / write operation. When A10 =H at this command, both banks are deactivated(precharge all, **PREA**).

## Auto-Refresh(REFA) [/RAS =/CAS =L, /WE =CKE =H]

REFA command starts auto-refresh cycle. Refresh address including bank address are generated internally. After this command, the banks are precharged automatically.

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

# **COMMAND TRUTH TABLE**

| COMMAND                                                 | MNEMONIC | CKE<br>n-1 | CKE<br>n | /S | /RAS | /CAS | /WE | BA0,1 | A11 | A10 | A0-9 |

|---------------------------------------------------------|----------|------------|----------|----|------|------|-----|-------|-----|-----|------|

| Deselect                                                | DESEL    | Н          | Х        | Н  | Х    | Х    | Х   | Х     | Х   | Х   | Х    |

| No Operation                                            | NOP      | Н          | Х        | L  | Н    | Н    | Н   | Х     | Х   | Х   | Х    |

| Row Adress Entry &<br>Bank Activate                     | ACT      | Η          | х        | L  | L    | Н    | Н   | V     | V   | V   | V    |

| Single Bank Precharge                                   | PRE      | Н          | Х        | L  | L    | Н    | L   | V     | Х   | L   | Х    |

| Precharge All Bank                                      | PREA     | Н          | Х        | L  | L    | Н    | L   | Х     | Х   | Н   | Х    |

| Column Address Entry<br>& Write                         | WRITE    | Н          | х        | L  | н    | L    | L   | V     | V   | L   | V    |

| Column Address Entry<br>& Write with Auto-<br>Precharge | WRITEA   | Н          | х        | L  | н    | L    | L   | V     | V   | н   | V    |

| Column Address Entry<br>& Read                          | READ     | Н          | х        | L  | Н    | L    | Н   | V     | V   | L   | V    |

| Column Address Entry<br>& Read with Auto<br>Precharge   | READA    | Η          | х        | L  | Н    | L    | Н   | V     | V   | H   | V    |

| Auto-Refresh                                            | REFA     | Н          | Н        | L  | L    | L    | Н   | Х     | Х   | Х   | Х    |

| Self-Refresh Entry                                      | REFS     | Н          | L        | L  | L    | L    | Н   | Х     | Х   | Х   | Х    |

| Self-Refresh Exit                                       | REFSX    | L          | Н        | Н  | Х    | Х    | Х   | Х     | Х   | Х   | Х    |

|                                                         |          | L          | Н        | L  | Н    | Н    | Н   | Х     | Х   | Х   | Х    |

| Burst Terminate                                         | TERM     | Н          | Х        | L  | Н    | Н    | L   | Х     | Х   | Х   | Х    |

| Mode Register Set                                       | MRS      | Н          | Х        | L  | L    | L    | L   | L     | L   | L   | V*1  |

H =High Level, L = Low Level, V = Valid, X = Don't Care, n = CK cycle number

#### NOTE:

1.A7-9 = 0, A0-6 = Mode Address

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

# **FUNCTION TRUTH TABLE**

| Current State | /S | /RAS | /CAS | /WE | Address              | Command      | Action                                                                    |

|---------------|----|------|------|-----|----------------------|--------------|---------------------------------------------------------------------------|

| IDLE          | Н  | Х    | Х    | Х   | Х                    | DESEL        | NOP                                                                       |

|               | L  | Н    | Н    | Н   | Х                    | NOP          | NOP                                                                       |

|               | L  | Н    | Н    | L   | BA                   | TBST         | ILLEGAL*2                                                                 |

|               | L  | Н    | L    | Х   | BA,CA,A10            | READ/WRITE   | ILLEGAL*2                                                                 |

|               | L  | L    | Н    | Н   | BA,RA                | ACT          | Bank Active,Latch RA                                                      |

|               | L  | L    | Н    | L   | BA,A10               | PRE/PREA     | NOP*4                                                                     |

|               | L  | L    | L    | Н   | Х                    | REFA         | Auto-Refresh*5                                                            |

|               | L  | L    | L    | L   | Op-Code,<br>Mode-Add | MRS          | Mode Register Set*5                                                       |

| ROW ACTIVE    | Н  | Х    | Х    | Х   | Х                    | DESEL        | NOP                                                                       |

|               | L  | Н    | Н    | Н   | Х                    | NOP          | NOP                                                                       |

|               | L  | Н    | Н    | L   | BA                   | TBST         | NOP                                                                       |

|               | L  | н    | L    | Н   | BA,CA,A10            | READ/READA   | Begin Read,Latch CA,<br>Determine Auto-Precharge                          |

|               |    |      |      |     | <b>DA OA A40</b>     | WRITE/       | Begin Write,Latch CA,                                                     |

|               | L  | Н    | L    | L   | BA,CA,A10            | WRITEA       | Determine Auto-Precharge                                                  |

|               | L  | L    | Н    | Н   | BA,RA                | ACT          | Bank Active/ILLEGAL*2                                                     |

|               | L  | L    | Н    | L   | BA,A10               | PRE/PREA     | Precharge/Precharge All                                                   |

|               | L  | L    | L    | Н   | Х                    | REFA         | ILLEGAL                                                                   |

|               | L  | L    | L    | L   | Op-Code,<br>Mode-Add | MRS          | ILLEGAL                                                                   |

| READ          | Н  | Х    | Х    | Х   | Х                    | DESEL        | NOP(Continue Burst to END)                                                |

|               | L  | Н    | Н    | Н   | Х                    | NOP          | NOP(Continue Burst to END)                                                |

|               | L  | Н    | Н    | L   | BA                   | TBST         | Terminate Burst                                                           |

|               | L  | Н    | L    | Н   | BA,CA,A10            | READ/READA   | Terminate Burst,Latch CA,<br>Begin New Read,Determine<br>Auto-Precharge*3 |

|               | L  | Н    | L    | L   | BA,CA,A10            | WRITE/WRITEA | Terminate Burst,Latch CA,<br>Begin Write,Determine Auto-<br>Precharge*3   |

|               | L  | L    | Н    | Н   | BA,RA                | ACT          | Bank Active/ILLEGAL*2                                                     |

|               | L  | L    | Н    | L   | BA,A10               | PRE/PREA     | Terminate Burst, Precharge                                                |

|               | L  | L    | L    | Н   | Х                    | REFA         | ILLEGAL                                                                   |

|               | L  | L    | L    | L   | Op-Code,<br>Mode-Add | MRS          | ILLEGAL                                                                   |

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

# **FUNCTION TRUTH TABLE**(continued)

| Current State | /S | /RAS                      | /CAS | /WE        | Address                                                                | Command          | Action                                                                  |

|---------------|----|---------------------------|------|------------|------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------|

| WRITE         | Н  | Х                         | Х    | Х          | Х                                                                      | DESEL            | NOP(Continue Burst to END)                                              |

|               | L  | Н                         | Н    | Н          | Х                                                                      | NOP              | NOP(Continue Burst to END)                                              |

|               | L  | Н                         | Н    | L          | BA                                                                     | TBST             | Terminate Burst                                                         |

|               | L  | H L H BA,CA,A10 READ/READ |      | READ/READA | Terminate Burst,Latch CA,<br>Begin Read,Determine Auto-<br>Precharge*3 |                  |                                                                         |

|               | L  | н                         | L    | L          | BA,CA,A10                                                              | WRITE/<br>WRITEA | Terminate Burst,Latch CA,<br>Begin Write,Determine Auto-<br>Precharge*3 |

|               | L  | L                         | Н    | Н          | BA,RA                                                                  | ACT              | Bank Active/ILLEGAL*2                                                   |

|               | L  | L                         | Н    | L          | BA,A10                                                                 | PRE/PREA         | Terminate Burst, Precharge                                              |

|               | L  | L                         | L    | Н          | Х                                                                      | REFA             | ILLEGAL                                                                 |

|               | L  | L                         | L    | L          | Op-Code,<br>Mode-Add                                                   | MRS              | ILLEGAL                                                                 |

| READ with     | Н  | Х                         | Х    | Х          | Х                                                                      | DESEL            | NOP(Continue Burst to END)                                              |

| AUTO          | L  | Н                         | Н    | Н          | Х                                                                      | NOP              | NOP(Continue Burst to END)                                              |

| PRECHARGE     | L  | Н                         | Н    | L          | BA                                                                     | TBST             | ILLEGAL                                                                 |

|               | L  | Н                         | L    | Н          | BA,CA,A10                                                              | READ/READA       | ILLEGAL                                                                 |

|               | L  | н                         | L    | L          | BA,CA,A10                                                              | WRITE/<br>WRITEA | ILLEGAL                                                                 |

|               | L  | L                         | Н    | Н          | BA,RA                                                                  | ACT              | Bank Active/ILLEGAL*2                                                   |

|               | L  | L                         | Н    | L          | BA,A10                                                                 | PRE/PREA         | ILLEGAL*2                                                               |

|               | L  | L                         | L    | Н          | Х                                                                      | REFA             | ILLEGAL                                                                 |

|               | L  | L                         | L    | L          | Op-Code,<br>Mode-Add                                                   | MRS              | ILLEGAL                                                                 |

| WRITE with    | Н  | Х                         | Х    | Х          | Х                                                                      | DESEL            | NOP(Continue Burst to END)                                              |

| AUTO          | Ц  | Н                         | Н    | Н          | Х                                                                      | NOP              | NOP(Continue Burst to END)                                              |

| PRECHARGE     | L  | Н                         | Н    | L          | BA                                                                     | TBST             | ILLEGAL                                                                 |

|               | L  | Н                         | L    | Н          | BA,CA,A10                                                              | READ/READA       | ILLEGAL                                                                 |

|               | L  | Н                         | L    | L          | BA,CA,A10                                                              | WRITE/<br>WRITEA | ILLEGAL                                                                 |

|               | L  | L                         | Н    | Н          | BA,RA                                                                  | ACT              | Bank Active/ILLEGAL*2                                                   |

|               | L  | L                         | Н    | L          | BA,A10                                                                 | PRE/PREA         | ILLEGAL*2                                                               |

|               | L  | L                         | L    | Н          | Х                                                                      | REFA             | ILLEGAL                                                                 |

|               | L  | L                         | L    | L          | Op-Code,<br>Mode-Add                                                   | MRS              | ILLEGAL                                                                 |

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

# **FUNCTION TRUTH TABLE**(continued)

| Current State | /S | /RAS | /CAS | /WE | Address              | Command    | Action                    |

|---------------|----|------|------|-----|----------------------|------------|---------------------------|

| PRE -         | Н  | Х    | Х    | Х   | Х                    | DESEL      | NOP(Idle after tRP)       |

| CHARGING      | L  | Н    | Н    | Н   | Х                    | NOP        | NOP(Idle after tRP)       |

|               | L  | Н    | Н    | L   | BA                   | TBST       | ILLEGAL*2                 |

|               | L  | Н    | L    | Х   | BA,CA,A10            | READ/WRITE | ILLEGAL*2                 |

|               | L  | L    | Н    | Н   | BA,RA                | ACT        | ILLEGAL*2                 |

|               | L  | L    | Н    | L   | BA,A10               | PRE/PREA   | NOP*4(Idle after tRP)     |

|               | L  | L    | L    | Н   | Х                    | REFA       | ILLEGAL                   |

|               | L  | L    | L    | L   | Op-Code,<br>Mode-Add | MRS        | ILLEGAL                   |

| ROW           | Н  | Х    | Х    | Х   | Х                    | DESEL      | NOP(Row Active after tRCD |

| ACTIVATING    | L  | Н    | Н    | Н   | Х                    | NOP        | NOP(Row Active after tRCD |

|               | L  | Н    | Н    | L   | BA                   | TBST       | ILLEGAL*2                 |

|               | L  | Н    | L    | Х   | BA,CA,A10            | READ/WRITE | ILLEGAL*2                 |

|               | L  | L    | Н    | Н   | BA,RA                | ACT        | ILLEGAL*2                 |

|               | L  | L    | Н    | L   | BA,A10               | PRE/PREA   | ILLEGAL*2                 |

|               | L  | L    | L    | Н   | Х                    | REFA       | ILLEGAL                   |

|               | L  | L    | L    | L   | Op-Code,<br>Mode-Add | MRS        | ILLEGAL                   |

| WRITE RE-     | Н  | Х    | Х    | Х   | Х                    | DESEL      | NOP                       |

| COVERING      | L  | Н    | Н    | Н   | Х                    | NOP        | NOP                       |

|               | L  | Н    | Н    | L   | BA                   | TBST       | ILLEGAL*2                 |

|               | L  | Н    | L    | Х   | BA,CA,A10            | READ/WRITE | ILLEGAL*2                 |

|               | L  | L    | Н    | Н   | BA,RA                | ACT        | ILLEGAL*2                 |

|               | L  | L    | Н    | L   | BA,A10               | PRE/PREA   | ILLEGAL*2                 |

|               | L  | L    | L    | Н   | Х                    | REFA       | ILLEGAL                   |

|               | L  | L    | L    | L   | Op-Code,<br>Mode-Add | MRS        | ILLEGAL                   |

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

# FUNCTION TRUTH TABLE(continued)

| Current State | /S | /RAS | /CAS | /WE | Address   | Command    | Action               |

|---------------|----|------|------|-----|-----------|------------|----------------------|

| RE-           | Н  | Х    | Х    | Х   | Х         | DESEL      | NOP(Idle after tRC)  |

| FRESHING      | L  | н    | Н    | Н   | Х         | NOP        | NOP(Idle after tRC)  |

|               | L  | н    | Н    | L   | BA        | TBST       | ILLEGAL              |

|               | L  | Н    | L    | Х   | BA,CA,A10 | READ/WRITE | ILLEGAL              |

|               | L  | L    | Н    | Н   | BA,RA     | ACT        | ILLEGAL              |

|               | L  | L    | Н    | L   | BA,A10    | PRE/PREA   | ILLEGAL              |

|               | L  | L    | L    | Н   | Х         | REFA       | ILLEGAL              |

|               | L  | L    | L    | L   | Op-Code,  | MRS        | ILLEGAL              |

|               | _  |      | _    | _   | Mode-Add  |            |                      |

| MODE          | Н  | Х    | Х    | Х   | Х         | DESEL      | NOP(Idle after tRSC) |

| REGISTER      | L  | н    | Н    | Н   | Х         | NOP        | NOP(Idle after tRSC) |

| SETTING       | L  | н    | Н    | L   | BA        | TBST       | ILLEGAL              |

|               | L  | н    | L    | Х   | BA,CA,A10 | READ/WRITE | ILLEGAL              |

|               | L  | L    | Н    | Н   | BA,RA     | ACT        | ILLEGAL              |

|               | L  | L    | Н    | L   | BA,A10    | PRE/PREA   | ILLEGAL              |

|               | L  | L    | L    | Н   | Х         | REFA       | ILLEGAL              |

|               | L  | L    | L    | L   | Op-Code,  | MRS        | ILLEGAL              |

|               | L  |      |      | L   | Mode-Add  | MILO       |                      |

#### ABBREVIATIONS:

H = Hige Level, L = Low Level, X = Don't Care

BA = Bank Address, RA = Row Address, CA = Column Address, NOP = No Operation

#### NOTES:

- 1. All entries assume that CKE was High during the preceding clock cycle and the current clock cycle.

- 2. ILLEGAL to bank in specified state; function may be legal in the bank indicated by BA, depending on the state of that bank.

- 3. Must satisfy bus contention, bus turn around, write recovery requirements.

- 4. NOP to bank precharging or in idle state. May precharge bank indicated by BA.

- 5. ILLEGAL if any bank is not idle.

ILLEGAL = Device operation and / or date-integrity are not guaranteed.

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

# **FUNCTION TRUTH TABLE FOR CKE**

| Current State | CKE<br>n-1 | CKE<br>n | /S | /RAS | /CAS | /WE | Add | Action                              |

|---------------|------------|----------|----|------|------|-----|-----|-------------------------------------|

| SELF -        | Н          | Х        | Х  | Х    | Х    | Х   | Х   | INVALID                             |

| REFRESH*1     | L          | Н        | Н  | Х    | Х    | Х   | Х   | Exit Self-Refresh(Idle after tRC)   |

|               | L          | Н        | L  | Н    | Н    | Н   | Х   | Exit Self-Refresh(Idle after tRC)   |

|               | L          | Н        | L  | Н    | Н    | L   | Х   | ILLEGAL                             |

|               | L          | Н        | L  | Н    | L    | Х   | Х   | ILLEGAL                             |

|               | L          | Н        | L  | L    | Х    | Х   | Х   | ILLEGAL                             |

|               | L          | L        | Х  | Х    | Х    | Х   | Х   | NOP(Maintain Self-Refresh)          |

| POWER         | Н          | Х        | Х  | Х    | Х    | Х   | Х   | INVALID                             |

| DOWN          | L          | Н        | Х  | Х    | Х    | Х   | Х   | Exit Power Down to Idle             |

|               | L          | L        | Х  | Х    | Х    | Х   | Х   | NOP(Maintain Self-Refresh)          |

| ALL BANKS     | Т          | Н        | Х  | Х    | Х    | Х   | Х   | Refer to Function Truth Table       |

| IDLE*2        | Т          | L        | L  | L    | L    | Н   | Х   | Enter Self-Refresh                  |

|               | н          | L        | Н  | Х    | Х    | Х   | Х   | Enter Power Down                    |

|               | Т          | L        | L  | Н    | Н    | Н   | Х   | Enter Power Down                    |

|               | Т          | L        | L  | Н    | Н    | L   | Х   | ILLEGAL                             |

|               | н          | L        | L  | Н    | L    | Х   | Х   | ILLEGAL                             |

|               | н          | L        | L  | L    | Х    | Х   | Х   | ILLEGAL                             |

|               | L          | Х        | Х  | Х    | Х    | Х   | Х   | Refer to Current State = Power Dowr |

| ANY STATE     | н          | Н        | Х  | Х    | Х    | Х   | Х   | Refer to Function Truth Table       |

| other than    | н          | L        | Х  | Х    | Х    | Х   | Х   | Begin CK0 Suspend at Next Cycle*3   |

| listed above  | L          | Н        | Х  | Х    | Х    | Х   | Х   | Exit CK0 Suspend at Next Cycle*3    |

|               | L          | L        | Х  | Х    | Х    | Х   | Х   | Maintain CK0 Suspend                |

#### ABBREVIATIONS:

H = High Level, L = Low Level, X = Don't Care

NOTES:

- 1. CKE Low to High transition will re-enable CK and other inputs **asynchronously**. A minimum setup time must be satisfied before any command other than EXIT.

- 2. Power-Down and Self-Refresh can be entered only from the All banks idle State.

- 3. Must be legal command.

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

# SIMPLIFIED STATE DIAGRAM

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

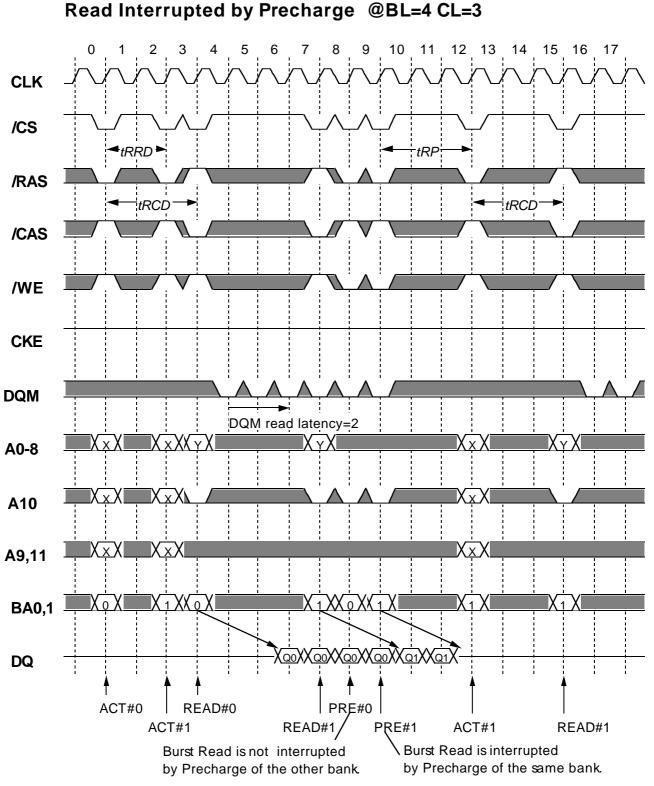

# POWER ON SEQUENCE

Before starting normal operation, the following power on sequence is necessary to prevent a SDRAM from damaged or malfunctioning.

- 1. Apply power and start clock. Attempt to maintain CKE high, DQMB0-7 high and NOP condition at the inputs.

- 2. Maintain stable power, stable clock, and NOP input conditions for a minimum of 200us.

- 3. Issue precharge commands for all banks. (PRE or PREA)

- 4. After all banks become idle state (after tRP), issue 8 or more auto-refresh commands.

- 5. Issue a mode register set command to initialize the mode register.

After these sequence, the SDRAM is idle state and ready for normal operation.

## MODE REGISTER

Burst Length, Burst Type and /CAS Latency can be programmed by setting the mode register(MRS). The mode register stores these date until the next MRS command, which may be issue when both banks are in idle state. After tRSC from a MRS command, the SDRAM is ready for new command.

|       |    |     |     |                                       |      |      |    |    |     |       |        |       |      |       | CK .        |      |       |  |

|-------|----|-----|-----|---------------------------------------|------|------|----|----|-----|-------|--------|-------|------|-------|-------------|------|-------|--|

|       |    |     |     |                                       |      |      |    |    |     |       |        |       |      |       | /S          |      |       |  |

| В     | A0 | BA1 | A11 | A10                                   | A9   | A8   | A7 | A6 | A5  | A4    | A3     | A2    | A1   | A0    | /RAS        |      |       |  |

|       |    |     | 1   |                                       |      |      |    |    |     |       |        |       |      |       | /CAS        |      |       |  |

|       | 0  | 0   | 0   | 0                                     | WM   | 0    | 0  | LT | MOE | Ε     | ΒТ     |       | BL   |       | /WE         |      |       |  |

|       |    |     |     | · · · · · · · · · · · · · · · · · · · |      |      |    |    |     |       |        |       |      | BA    | 0,1 A11-0 [ |      | V     |  |

|       |    |     |     |                                       |      |      |    |    |     |       |        |       |      | BL    | BT= 0       |      | BT= 1 |  |

|       |    |     |     |                                       |      |      |    |    |     |       |        |       |      | 000   | 1           |      | 1     |  |

|       |    |     |     |                                       |      |      |    |    |     |       |        |       |      | 001   | 2           |      | 2     |  |

|       |    | CL  |     | /CAS                                  | S LA | ΓΕΝΟ | CY |    |     | BURST |        |       | 010  | 4     | 4           |      |       |  |

|       |    | 000 | )   |                                       | F    | २    |    |    |     |       |        |       | 011  | 8     |             | 8    |       |  |

|       |    | 001 |     |                                       | F    | २    |    |    |     |       | LENGTH |       | H    | 100   | R           |      | R     |  |

|       |    | 010 | )   |                                       | 2    | 2    |    |    |     |       |        |       |      | 101   | R           |      | R     |  |

|       |    | 011 |     |                                       | 3    | 3    |    |    |     |       |        |       |      | 110   | R           |      | R     |  |

| MODE  |    | 100 | )   |                                       | F    | २    |    |    |     |       |        |       |      | 111   | FP          |      | R     |  |

|       |    | 101 |     |                                       | F    | २    |    |    |     |       |        |       |      |       |             |      |       |  |

|       |    | 110 | )   |                                       | F    | २    |    |    |     |       | ΒL     | IRST  |      | 0     | SEQUE       |      |       |  |

|       |    | 111 |     |                                       | F    | २    |    |    |     |       | T      | YPE   |      | 1     | INTERL      | EAVE | D     |  |

| WRITE |    | 0   | В   | URS                                   | т    |      |    |    |     |       | R:F    | Rese  | erve | d for | Future Us   | se   |       |  |

| MODE  |    | 1   |     | INGL                                  |      | Т    |    |    |     |       | FΡ     | : Ful | l Pa | ge    |             |      |       |  |

Some contents are subject to change without notice.

#### **MITSUBISHI LSIs**

# MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

| Initial Address BL Column Addressin |    |    |   |   |   |   | essing | )      |    |   |   |   |   |             |   |   |   |   |   |  |

|-------------------------------------|----|----|---|---|---|---|--------|--------|----|---|---|---|---|-------------|---|---|---|---|---|--|

| A2                                  | A1 | A0 |   |   |   |   | Sequ   | uentia | al |   |   |   |   | Interleaved |   |   |   |   |   |  |

| 0                                   | 0  | 0  |   | 0 | 1 | 2 | 3      | 4      | 5  | 6 | 7 | 0 | 1 | 2           | 3 | 4 | 5 | 6 | 7 |  |

| 0                                   | 0  | 1  |   | 1 | 2 | 3 | 4      | 5      | 6  | 7 | 0 | 1 | 0 | 3           | 2 | 5 | 4 | 7 | 6 |  |

| 0                                   | 1  | 0  |   | 2 | 3 | 4 | 5      | 6      | 7  | 0 | 1 | 2 | 3 | 0           | 1 | 6 | 7 | 4 | 5 |  |

| 0                                   | 1  | 1  | 0 | 3 | 4 | 5 | 6      | 7      | 0  | 1 | 2 | 3 | 2 | 1           | 0 | 7 | 6 | 5 | 4 |  |

| 1                                   | 0  | 0  | 8 | 4 | 5 | 6 | 7      | 0      | 1  | 2 | 3 | 4 | 5 | 6           | 7 | 0 | 1 | 2 | 3 |  |

| 1                                   | 0  | 1  |   | 5 | 6 | 7 | 0      | 1      | 2  | 3 | 4 | 5 | 4 | 7           | 6 | 1 | 0 | 3 | 2 |  |

| 1                                   | 1  | 0  |   | 6 | 7 | 0 | 1      | 2      | 3  | 4 | 5 | 6 | 7 | 4           | 5 | 2 | 3 | 0 | 1 |  |

| 1                                   | 1  | 1  |   | 7 | 0 | 1 | 2      | 3      | 4  | 5 | 6 | 7 | 6 | 5           | 4 | 3 | 2 | 1 | 0 |  |

| -                                   | 0  | 0  |   | 0 | 1 | 2 | 3      |        |    |   |   | 0 | 1 | 2           | 3 |   |   |   |   |  |

| -                                   | 0  | 1  | 4 | 1 | 2 | 3 | 0      |        |    |   |   | 1 | 0 | 3           | 2 |   |   |   |   |  |

| -                                   | 1  | 0  | 4 | 2 | 3 | 0 | 1      |        |    |   |   | 2 | 3 | 0           | 1 |   |   |   |   |  |

| -                                   | 1  | 1  |   | 3 | 0 | 1 | 2      |        |    |   |   | 3 | 2 | 1           | 0 |   |   |   |   |  |

| -                                   | -  | 0  | 2 | 0 | 1 |   |        |        |    |   |   | 0 | 1 |             |   |   |   |   |   |  |

| -                                   | -  | 1  | 2 | 1 | 0 |   |        |        |    |   |   | 1 | 0 |             |   |   |   |   |   |  |

Some contents are subject to change without notice.

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

### **OPERATION DESCRIPTION**

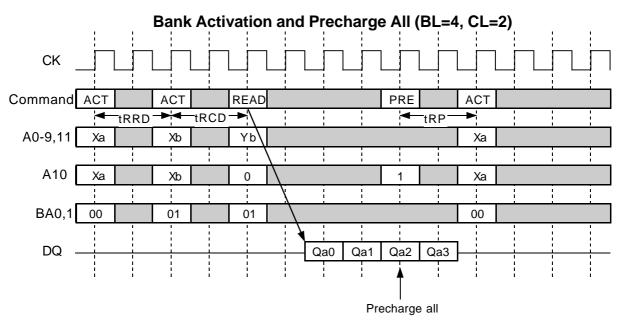

#### BANK ACTIVATE

One of four banks is activated by an ACT command.

An bank is selected by BA0-1. A row is selected by A0-11.

Multiple banks can be active state concurrently by issuing multiple ACT commands.

Minimum activation interval between one bank and another bank is tRRD.

#### PRECHARGE

An open bank is deactivated by a PRE command.

A bank to be deactivated is designated by BA0-1.

When multiple banks are active, a precharge all command (PREA, PRE + A10=H)

deactivates all of open banks at the same time. BA0-1 are "Don't Care" in this case.

Minimum delay time of an ACT command after a PRE command to the same bank is tRP.

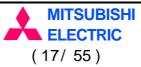

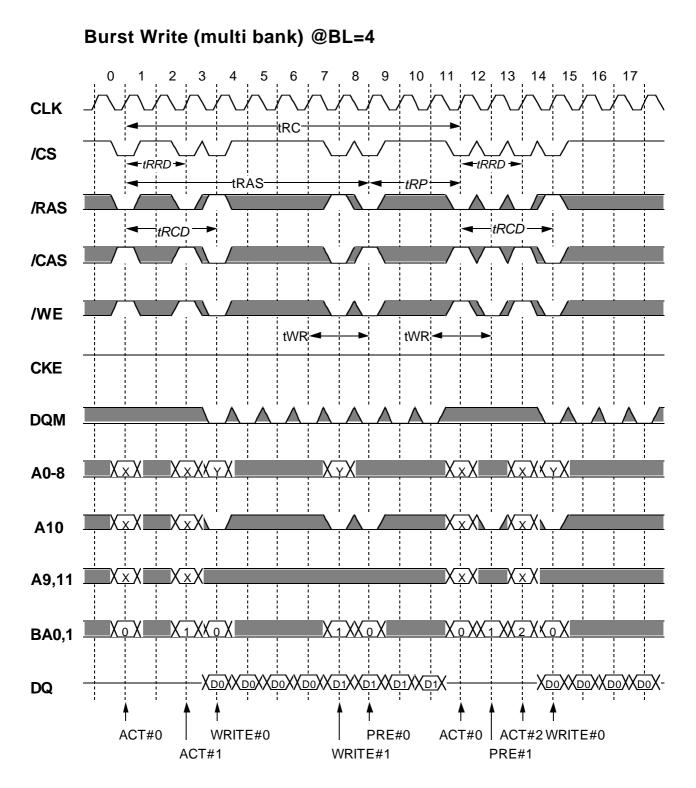

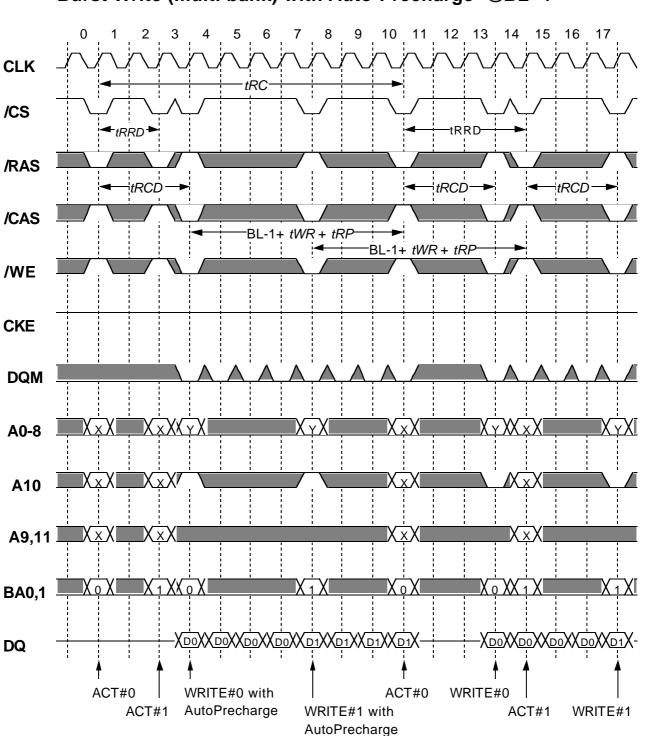

#### READ

A READ command can be issued to any active bank. The start address is specified by A0-9 (x8) . 1st output data is available after the /CAS Latency from the READ. The consecutive data length is defined by the Burst Length. The address sequence of the burst data is defined by the Burst Type. Minimum delay time of a READ command after an ACT command to the same bank is tRCD.

When A10 is high at a READ command, auto-precharge (READA) is performed. Any command (READ, WRITE, PRE, ACT, TBST) to the same bank is inhibited till the internal precharge is complete. The internal precharge starts at the BL after READA. The next ACT command can be issued after (BL + tRP) from the previous READA. In any case, tRCD+BL  $\geq$  tRASmin must be met.

Some contents are subject to change without notice.

**MITSUBISHI LSIs**

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

# MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

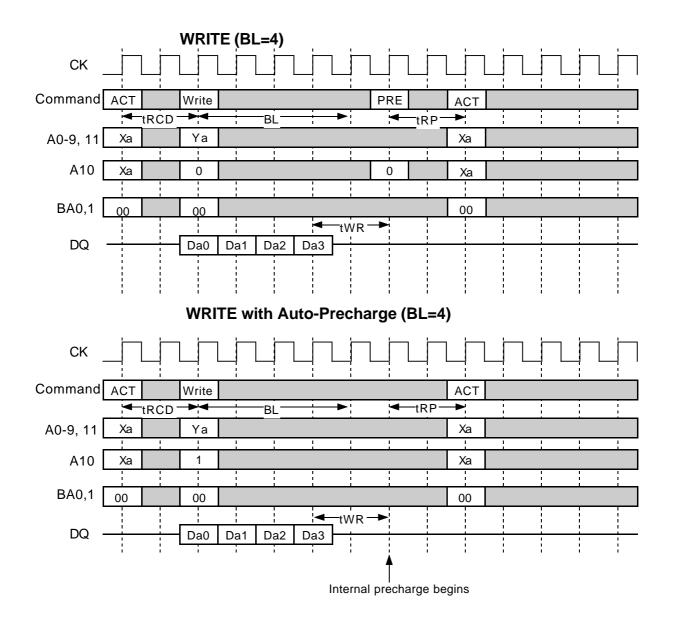

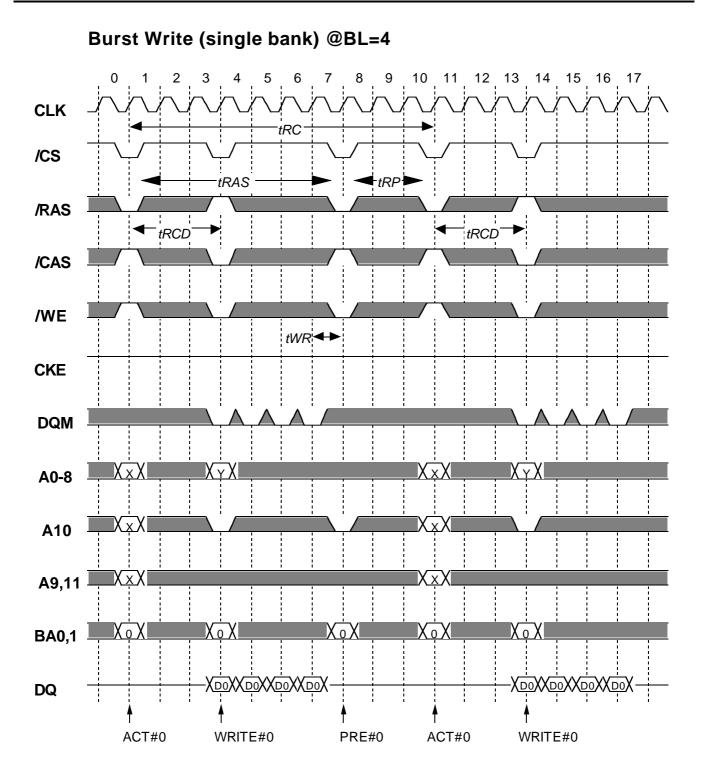

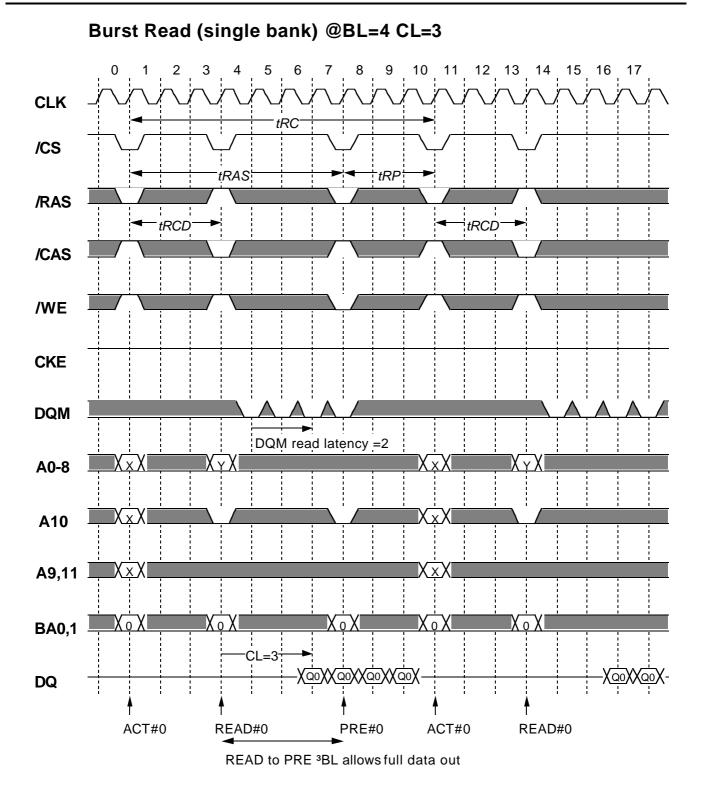

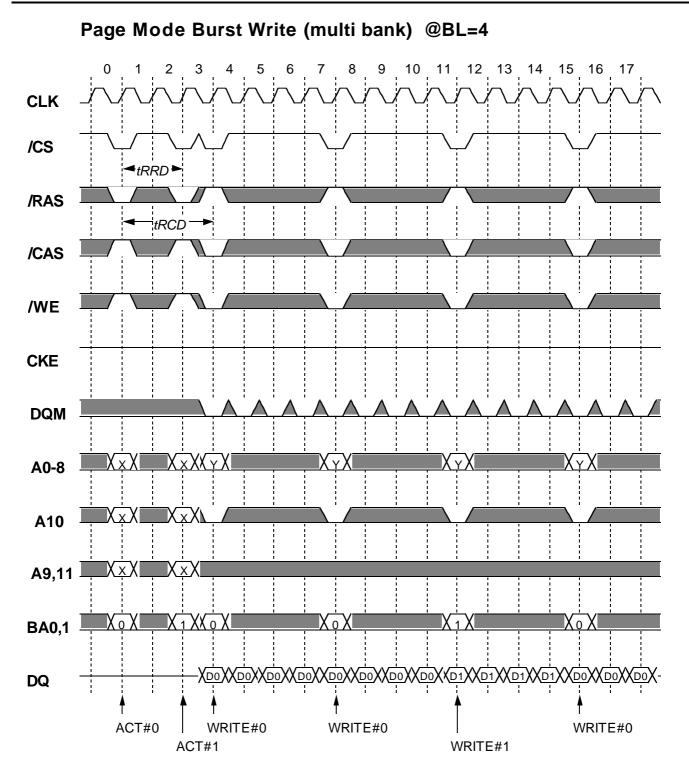

#### WRITE

A WRITE command can be issued to any active bank. The start address is specified by A0-9 (x8). 1st input data is set at the same cycle as the WRITE. The consecutive data length to be written is defined by the Burst Length. The address sequence of burst data is defined by the Burst Type. Minimum delay time of a WRITE command after an ACT command to the same bank is tRCD. From the last input data to the PRE command, the write recovery time (tWR) is required. When A10 is high at a WRITE command, auto-precharge (WRITEA) is performed. Any command (READ, WRITE, PRE, ACT, TBST) to the same bank is inhibited till the internal precharge is complete. The internal precharge starts at tWR after the last input data cycle. The next ACT command can be issued after (BL + tWR -1 + tRP) from the previous WRITEA. In any case, tRCD + BL + tWR -1  $\geq$  tRASmin must be met.

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

# BURST INTERRUPTION

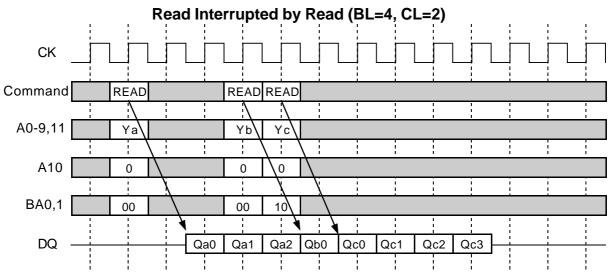

#### [Read Interrupted by Read]

Burst read oparation can be interrupted by new read of the same or the other bank. Random column access is allowed READ to READ interval is minimum 1 CK

#### [Read Interrupted by Write]

Burst read operation can be interrupted by write of any active bank. Random column access is allowed. In this case, the DQ should be controlled adequately by using the DQMB0-7 to prevent the bus contention. The output is disabled automatically 1 cycle after WRITE assertion.

Some contents are subject to change without notice.

# MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

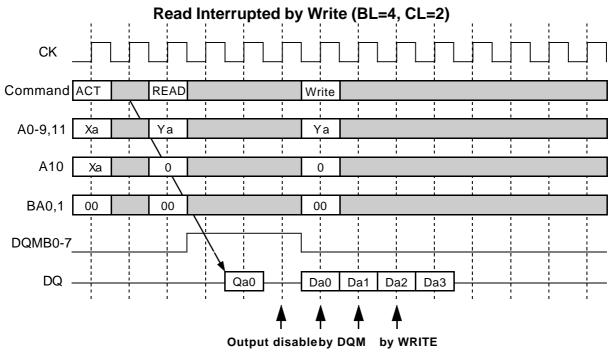

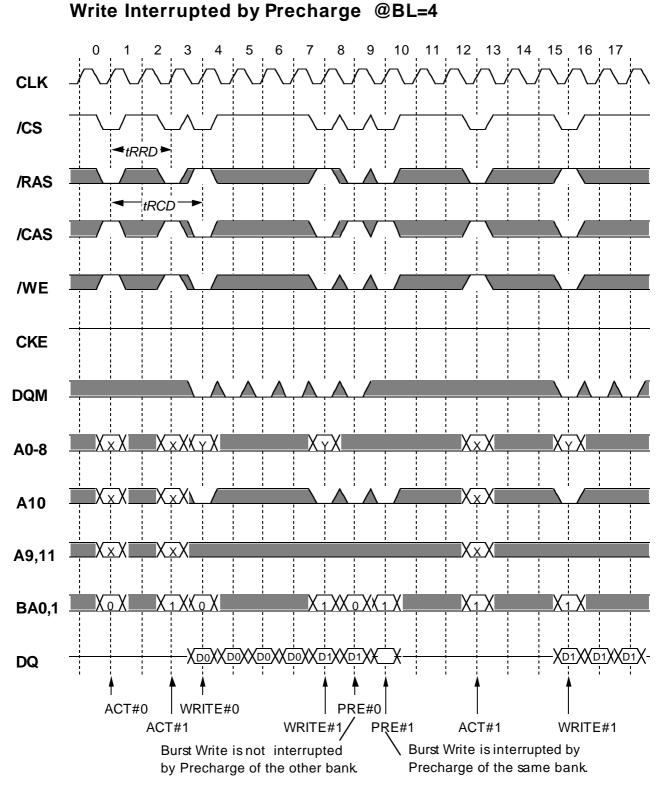

#### [Read Interrupted by Precharge]

A burst read operation can be interrupted by precharge of *the same bank*. Read to PRE interval is minimum 1 CK. A PRE command output disable latency is equivalent to the /CAS Latency.

Some contents are subject to change without notice.

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

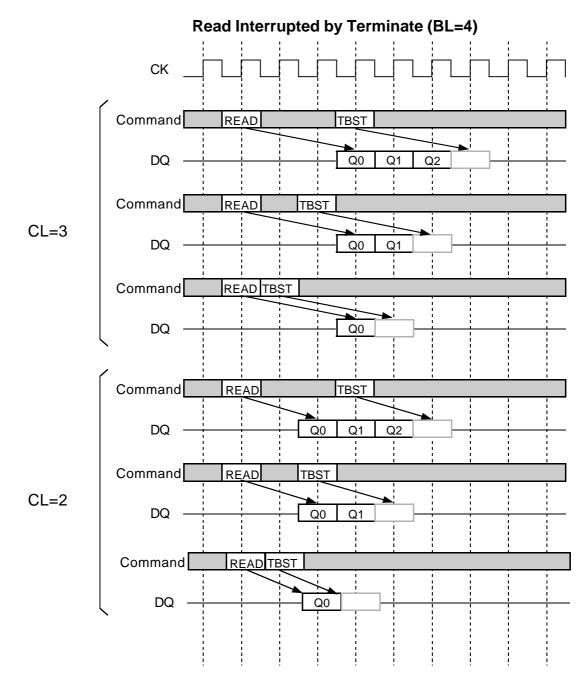

#### [Read Interrupted by Burst Terminate]

Similarly to the precharge, burst terminate command can interrupt burst read operation and disable the data output. The terminated bank remains active,READ to TBST interval is minimum of 1 CK. A TBSTcommand to output disable latency is equivalent to the /CAS Latency.

Some contents are subject to change without notice.

#### **MITSUBISHI LSIs**

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

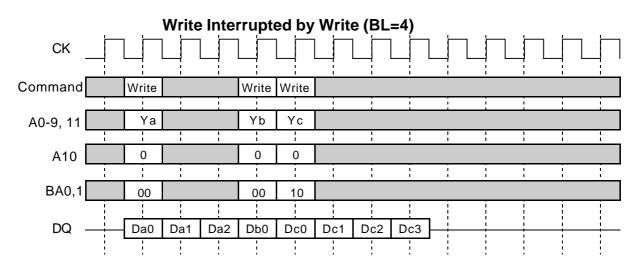

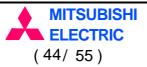

#### [Write Interrupted by Write]

Burst write operation can be interrupted by new write of any active bank. Random column access is allowed. WRITE to WRITE interval is minimum 1 CK.

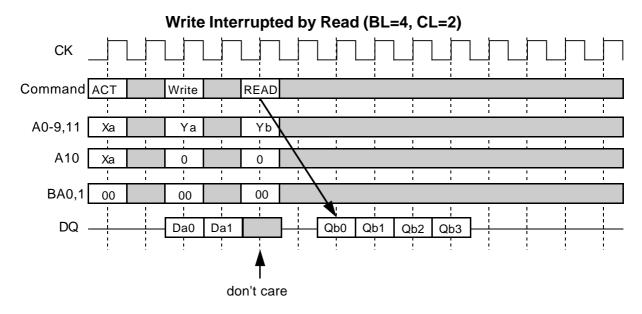

#### [Write Interrupted by Read]

Burst write operation can be interrupted by read of any active bank. Random column access is allowed. WRITE to READ interval is minimum 1 CK. The input data on DQ at the interrupting READ cycle is "don't care".

Some contents are subject to change without notice.

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

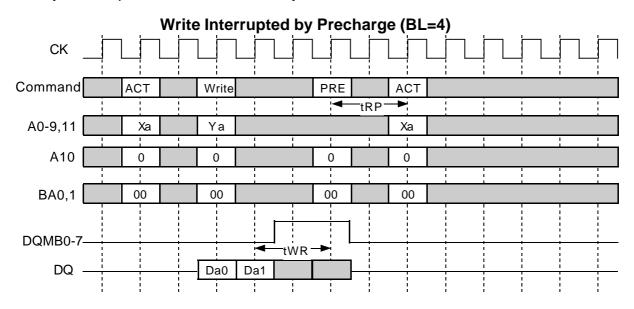

#### [Write Interrupted by Precharge]

Burst write operation can be interrupted by precharge of *the same bank*. Write recovery time(tWR) is required from the last data to PRE command. During write recovery, data inputs must be masked by DQM.

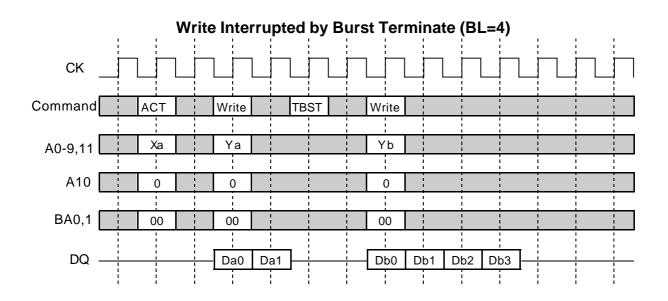

#### [Write Interrupted by Burst Terminate]

Burst terminate command can terminate burst write operation. In this case, the write recovery time is not required and the bank remains active. The WRITE to TBST minimum interval is 1CK.

Some contents are subject to change without notice.

#### **MITSUBISHI LSIs**

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

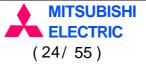

### [Write with Auto-Precharge interrupted by Write or Read to anotehr Bank]

Burst write with auto-precharge can be interrupted by write or read to *another bank*. Next ACT command can be issued after (BL+tWR-1+tRP) from the WRITEA. Autoprecharge interrrupted by a command to the same bank is inhibited.

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

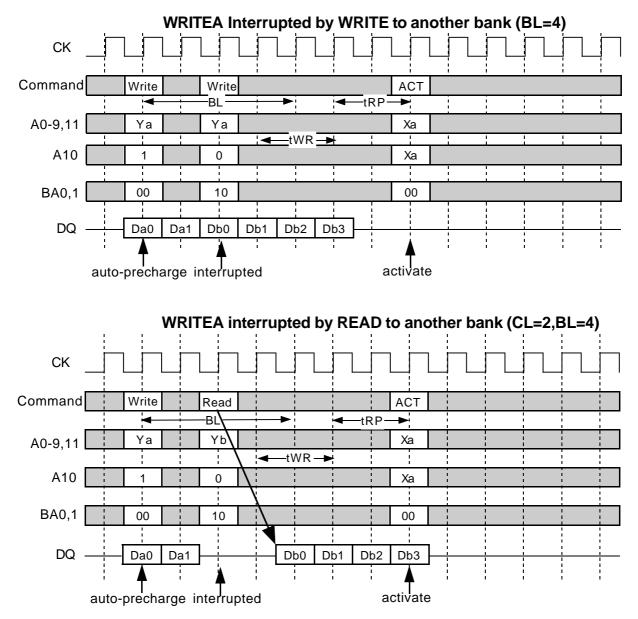

#### [Read with Auto-Precharge interrupted by Read to anotehr Bank]

Burst read with auto-precharge can be interrupted by read to *another bank*. Next ACT command can be issued after (BL+tRP) from the READA. Auto-precharge interrrupted by a command to the same bank is inhibited.

#### **Full Page Burst**

Full page burst length is available for only the sequential burst type. Full page burst read or write is repeated untill aPrecharge or a Burst Terminate command is issued. In case of the full page burst, a read or write with auto-precharge command is illegal.

#### Single Write

When single write mode is set, burst length for write is always one, independently of Burst Length defined by (A2-0).

# MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

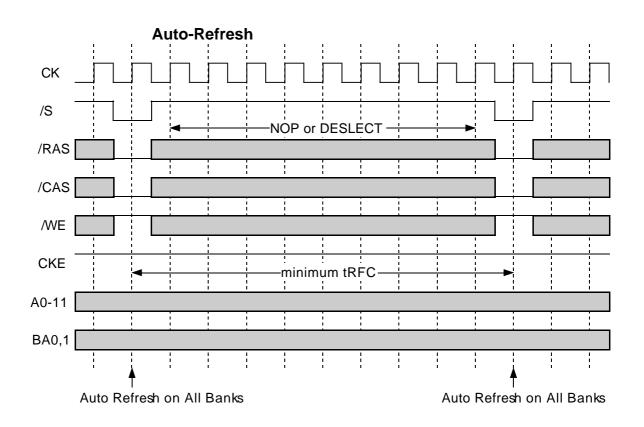

#### **AUTO REFRESH**

Single cycle of auto-refresh is initiated with a REFA(/CS=/RAS=/CAS=L, /WE=/CKE=H) command. The refresh address is generated internally. 4096 REFA cycle within 64ms refresh 128Mbit memory cells. The auto-refresh is performed on 4banks concurrently. Before performing an auto-refresh, all banks must be in the idle state. Auto-refresh to auto-refresh interval is minimum tRFC. Any command must not be issued before tRFC from the REFA command.

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

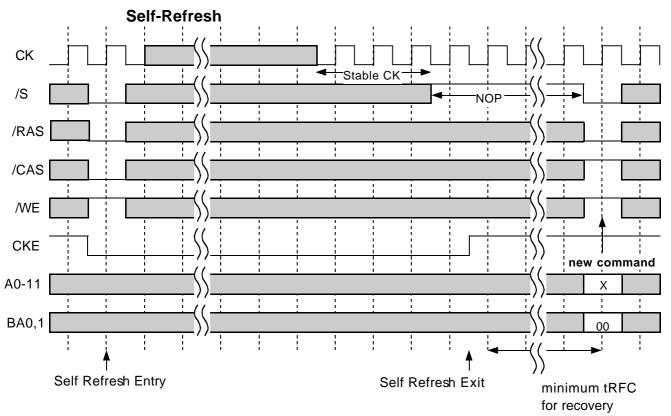

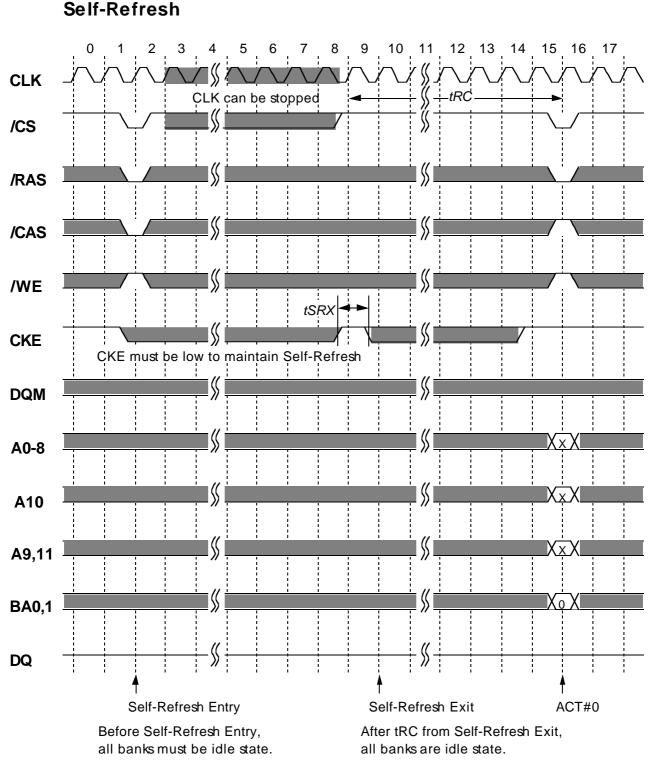

#### SELF REFRESH

Self-refresh mode is entered by issuing a REFS command (/CS=/RAS=/CAS=L, /WE=H, CKE=L). Once the self-refresh is initiated, it is maintained as log as CKE is kept low.During the self-refresh mode, CKE is asynchronous and the only enabled input , all other inputs including CK are disabled and ignored, so that power consumption due to synchronous inputs is saved. To exit the self-refresh, supplying stable CK inputs, asserting DESEL or NOP command and then asserting CKE=H. After tRFC from the 1st CK edge follwing CKE=H, all banks are in the idle state and a new command can be issued after, but DESEL or NOP commands must be asserted till then.

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

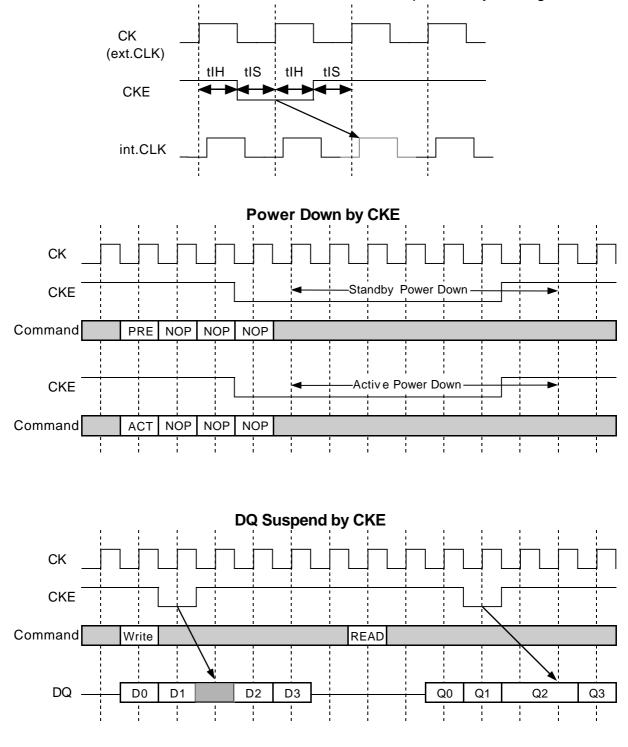

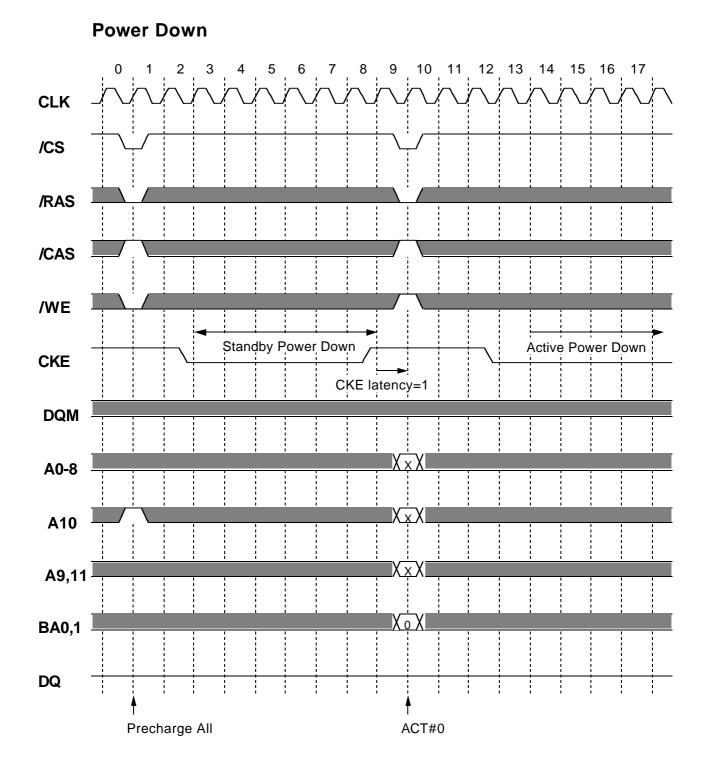

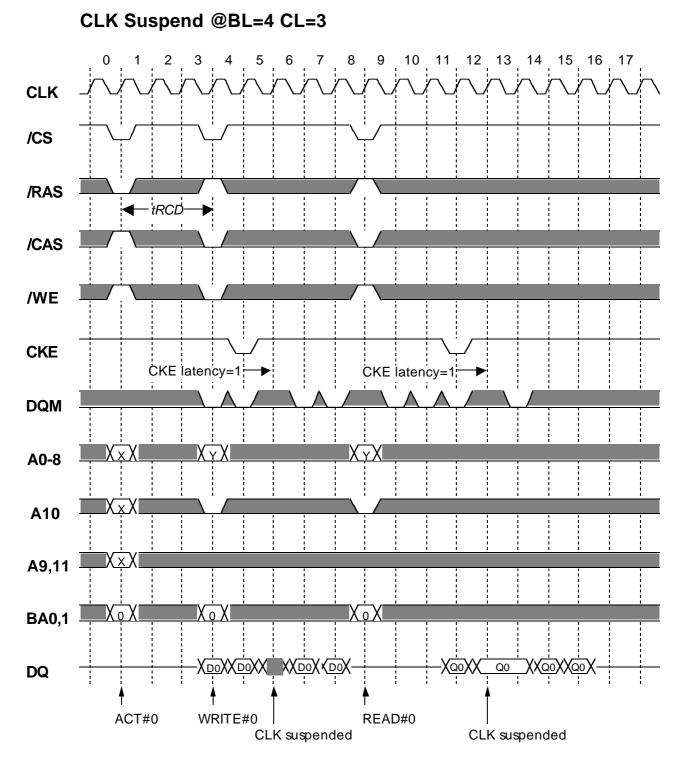

#### CLK SUSPEND and POWER DOWN

CKE controls the internal CLK at the following cycle. Figure below shows how CKE works. By negating CKE, the next internal CLK is suspended. The purpose of CLK suspend is power down, output suspend or input suspend. CKE is a synchronous input except during the self-refresh mode. CLK suspend can be performed either when the banks are active or idle. A command at the suspended cycle is ignored.

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

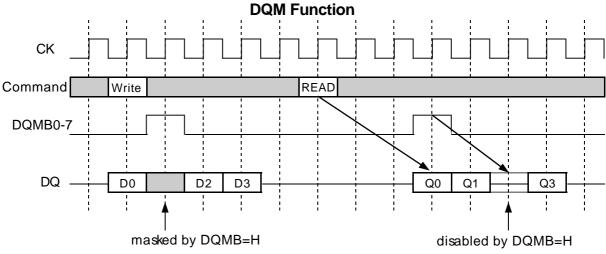

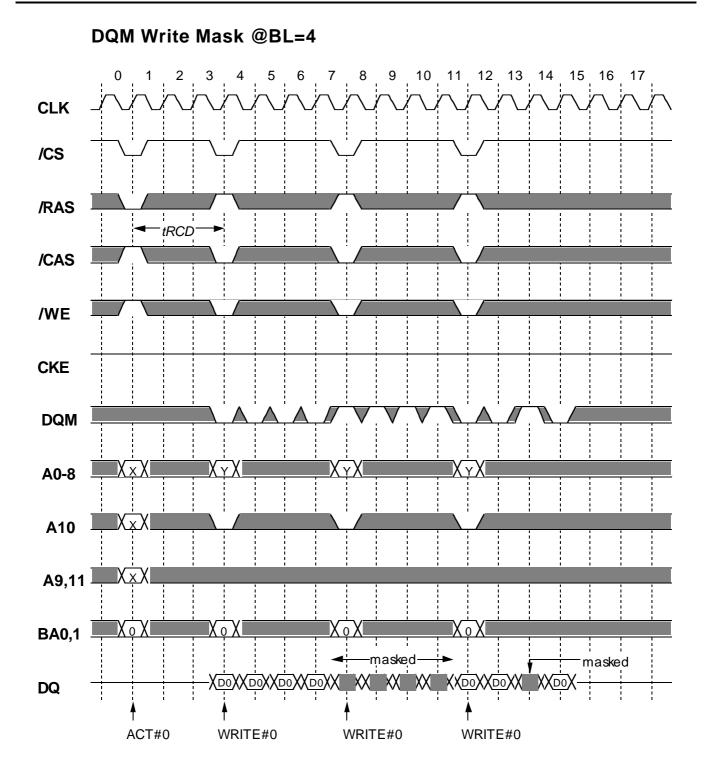

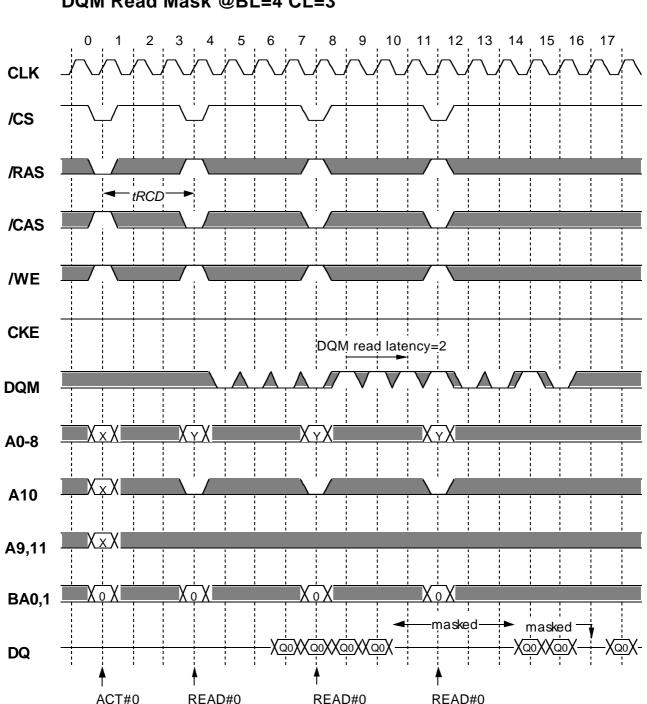

#### DQM CONTROL

DQMB0-7 is a dual function signal defined as the data mask for writes and the output disable for reads. During writes, DQMB0-7 masks input data word by word. DQMB0-7 to Data In latency is 0.

During reads, DQMB0-7 forces output to Hi-Z word by word. DQMB0-7 to output Hi-Z latency is 2.

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol | Parameter             | Condition           | Ratings        | Unit |

|--------|-----------------------|---------------------|----------------|------|

| Vdd    | Supply Voltage        | with respect to Vss | -0.5 ~ 4.6     | V    |

| VI     | Input Voltage         | with respect to Vss | -0.5 ~ Vdd+0.5 | V    |

| VO     | Output Voltage        | with respect to Vss | -0.5 ~ Vdd+0.5 | V    |

| IO     | Output Current        |                     | 50             | mA   |

| Pd     | Power Dissipation     | Ta=25°C             | 9              | W    |

| Topr   | Operating Temperature |                     | 0 ~ 70         | °C   |

| Tstg   | Storage Temperature   |                     | -40 ~ 100      | °C   |

# **RECOMMENDED OPERATING CONDITION**

(Ta=0 ~ 70°C, unless otherwise noted)

| Sumbol | Parameter                           |      |      |         |      |

|--------|-------------------------------------|------|------|---------|------|

| Symbol | i arameter                          | Min. | Тур. | Max.    | Unit |

| Vdd    | Supply Voltage                      | 3.0  | 3.3  | 3.6     | V    |

| Vss    | Supply Voltage                      | 0    | 0    | 0       | V    |

| VIH    | High-Level Input Voltage all inputs | 2.0  |      | Vdd+0.3 | V    |

| VIL    | Low-Level Input Voltage all inputs  | -0.3 |      | 0.8     | V    |

Note)

1:VIH(max)=5.5V for pulse width less than 10ns.

2.VIL(min)=-1.0 for pulse width less than 10ns.

#### **CAPACITANCE**

$(Ta=0 \sim 70^{\circ}C, Vdd = 3.3 \pm 0.3V, Vss = 0V, unless otherwise noted)$

| Symbol | Parameter                        | Test Condition     | Limits(max.) | Unit |

|--------|----------------------------------|--------------------|--------------|------|

| CI(A)  | Input Capacitance, address pin   |                    | 60           | pF   |

| CI(C)  | Input Capacitance, /RAS,/CAS,/WE | @1MHz<br>1.4V bias | 60           | pF   |

| CI(K)  | Input Capacitance, CK pin        | 200mV swing        | 40           | pF   |

| CI/O   | Input Capacitance, I/O pin       |                    | 16.5         | pF   |

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

# AVERAGE SUPPLY CURRENT from Vdd

(Ta=0 ~70°C, Vdd =  $3.3 \pm 0.3$ V, Vss = 0V, unless otherwise noted)

| Parameter                                       | Symbol                                                                                                                                                                                                                | Test Condition                                  | Lir<br>(m |        |      |

|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------|--------|------|

| i arameter                                      | le bank active (discrete) Icc1 tRC=min.tCLK=min, BL=1,CL=3   echarge stanby Icc2P CKE=L,tCLK=15ns, /CS>Vcc-0.2V   irrent Icc2PS CKE=CLK=L, /CS>Vcc-0.2V   power-down mode Icc2N CKE=H,tCLK=15ns,VIH>Vcc-0.2V,VIL<0.2V |                                                 | -6        | -7, -8 | Unit |

| operating current<br>one bank active (discrete) | lcc1                                                                                                                                                                                                                  | tRC=min.tCLK=min, BL=1,CL=3                     | 990       | 900    | mA   |

| precharge stanby<br>current                     | Icc2P                                                                                                                                                                                                                 | CKE=L,tCLK=15ns, /CS>Vcc-0.2V                   | 36        | 36     | mA   |

| in power-down mode                              | Icc2PS                                                                                                                                                                                                                | CKE=CLK=L, /CS>Vcc-0.2V                         | 18        | 18     | mA   |

| precharge stanby current                        | lcc2N                                                                                                                                                                                                                 | CKE=H,tCLK=15ns,VIH>Vcc-0.2V,VIL<0.2V           | 225       | 225    | mA   |

| in non power-down mode                          | Icc2NS                                                                                                                                                                                                                | CKE=H,CLK=L,VIH>Vcc-0.2V,VIL<0.2V(fixed)        | 135       | 135    | mA   |

| active stanby current<br>in non power-down mode | lcc3N                                                                                                                                                                                                                 | CKE=H,tCLK=15ns                                 | 270       | 270    | mA   |

| one bank active (discrete)                      | Icc3NS                                                                                                                                                                                                                | CKE=H,CLK=L                                     | 180       | 180    | mA   |

| burst current                                   | Icc4                                                                                                                                                                                                                  | tCLK=min, BL=4, CL=3,all banks active(discerte) | 1350      | 1080   | mA   |

| auto-refresh current                            | lcc5                                                                                                                                                                                                                  | tRC=min, tCLK=min                               | 1440      | 1440   | mA   |

| self-refresh current                            | lcc6                                                                                                                                                                                                                  | CKE <0.2V                                       | 18        | 18     | mA   |

Note)

1:Icc(max) is specified at the output open condition.

# **AC OPERATING CONDITIONS AND CHARACTERISTICS**

$(Ta=0 \sim 70^{\circ}C, Vdd = 3.3 \pm 0.3V, Vss = 0V, unless otherwise noted)$

|         | _                             |                       | Lim  |      |      |

|---------|-------------------------------|-----------------------|------|------|------|

| Symbol  | Parameter                     | Test Condition        | Min. | Max. | Unit |

| VOH(DC) | High-Level Output Voltage(DC) | IOH=-2mA              | 2.4  |      | V    |

| VOL(DC) | Low-Level Output Voltage(DC)  | IOL=2mA               |      | 0.4  | V    |

| IOZ     | Off-stare Output Current      | Q floating VO=0 ~ Vdd | -10  | 10   | uA   |

| li      | Input Current                 | VIH=0 ~ Vdd+0.3V      | -90  | 90   | uA   |

Some contents are subject to change without notice.

**MITSUBISHI LSIs**

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

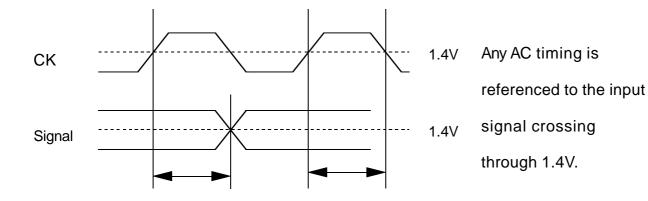

# AC TIMING REQUIREMENTS (SDRAM Component)

(Ta=0 ~ 70°C, Vdd =  $3.3 \pm 0.3$ V, Vss = 0V, unless otherwise noted) Input Pulse Levels: 0.8V to 2.0V Input Timing Measurement Level: 1.4V

|        |                              |          |      |      | Lim  | nits |      |      |      |

|--------|------------------------------|----------|------|------|------|------|------|------|------|

| Symbol | Parameter                    |          | -6   | 6    | -7   | 7    |      | -8   | Unit |

|        |                              |          | Min. | Max. | Min. | Max. | Min. | Max. |      |

| tCLK   | CK cycle time                | CL=2     | 10   |      | 10   |      | 13   |      | ns   |

|        |                              | CL=3     | 7.5  |      | 10   |      | 10   |      | ns   |

| tCH    | CK High pulse width          | 2.5      |      | 3    |      | 3    |      | ns   |      |

| tCL    | CK Low pilse width           | 2.5      |      | 3    |      | 3    |      | ns   |      |

| tT     | Transition time of CK        | 1        | 10   | 1    | 10   | 1    | 10   | ns   |      |

| tIS    | Input Setup time(all inputs) |          | 1.5  |      | 2    |      | 2    |      | ns   |

| tIH    | Input Hold time(all inp      | 0.8      |      | 1    |      | 1    |      | ns   |      |

| tRC    | Row cycle time               |          | 67.5 |      | 70   |      | 70   |      | ns   |

| tRCD   | Row to Column Delay          | /        | 20   |      | 20   |      | 20   |      | ns   |

| tRAS   | Row Active time              |          | 45   | 100K | 50   | 100K | 50   | 100K | ns   |

| tRP    | Row Precharge time           |          | 20   |      | 20   |      | 20   |      | ns   |

| tWR    | Write Recovery time          |          | 15   |      | 20   |      | 20   |      | ns   |

| tRRD   | Act to Act Deley time        |          | 15   |      | 20   |      | 20   |      | ns   |

| tRSC   | Mode Register Set Cy         | cle time | 15   |      | 20   |      | 20   |      | ns   |

| tSRX   | Self Refresh Exit time       | 7.5      |      | 10   |      | 10   |      | ns   |      |

| tPDE   | Power Down Exit time         | 7.5      |      | 10   |      | 10   |      | ns   |      |

| tREF   | Refresh Interval time        |          |      | 64   |      | 64   |      | 64   | ms   |

**MITSUBISHI**

**ELECTRIC**

(33/55)

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

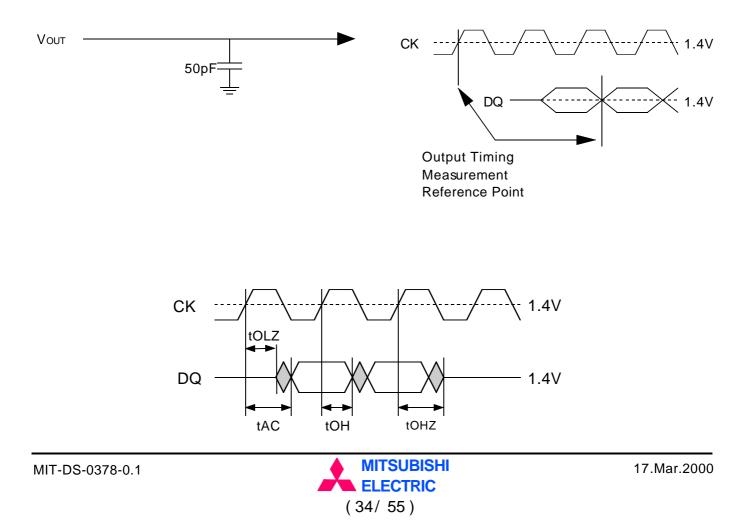

# SWITCHING CHARACTERISTICS (SDRAM Component)

$(Ta=0 \sim 70^{\circ}C, Vdd = 3.3 \pm 0.3V, Vss = 0V, unless otherwise note3)$

|        |                                             |      |      |      | Lim  | Limits |      |      |      |  |  |

|--------|---------------------------------------------|------|------|------|------|--------|------|------|------|--|--|

| Symbol | Parameter -6 -7                             |      |      | 3    | Unit |        |      |      |      |  |  |

|        |                                             |      | Min. | Max. | Min. | Max.   | Min. | Max. | Onit |  |  |

| tAC    | Access time from CK                         | CL=2 |      | 6    |      | 6      |      | 7    | ns   |  |  |

|        |                                             | CL=3 |      | 5.4  |      | 6      |      | 6    | ns   |  |  |

| tOH    | Output Hold time<br>from CK                 | CL=2 | 3    |      | 3    |        | 3    |      | ns   |  |  |

|        |                                             | CL=3 | 2.7  |      | 3    |        | 3    |      | ns   |  |  |

| tOLZ   | Delay time, output low<br>impedance from CK |      | 0    |      | 0    |        | 0    |      | ns   |  |  |

| tOHZ   | Delay time, output high impedance from CK   |      | 2.7  | 5.4  | 3    | 6      | 3    | 6    | ns   |  |  |

Note)

1 If clock rising time is longer than 1ns,(tT/2-0.5)ns should be added to parameter.

#### **Output Load Condition**

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

Italic parameter indicates minimum case

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

Italic parameter indicates minimum case

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

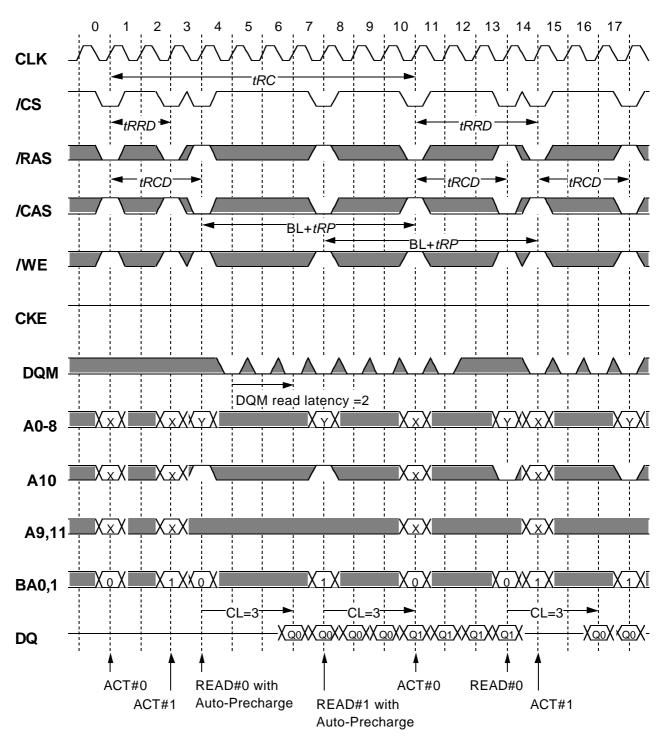

## Burst Read (multiple bank) @BL=4 CL=3

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

Burst Write (multi bank) with Auto-Precharge @BL=4

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

## Burst Read (multiple bank) with Auto-Precharge @BL=4 CL=3

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

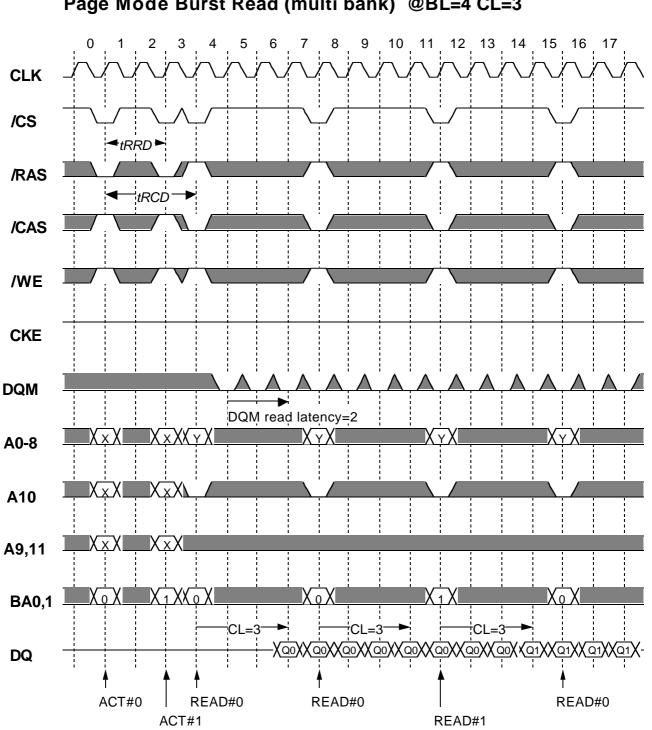

### Page Mode Burst Read (multi bank) @BL=4 CL=3

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

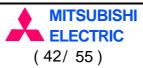

## Write Interrupted by Write / Read @BL=4

Burst Write can be interrupted by Write or Read of any active bank.

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

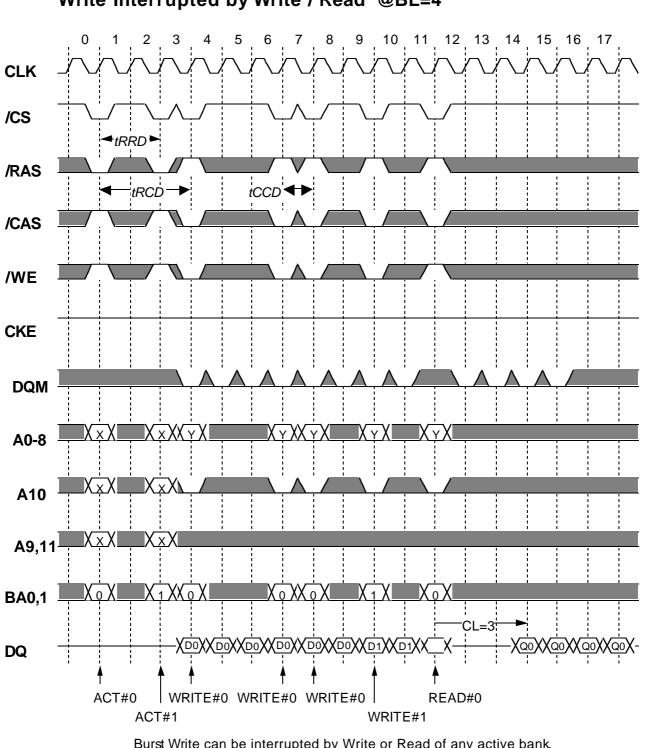

#### Read Interrupted by Read / Write @BL=4 CL=3

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

Auto-Refresh @BL=4

**MITSUBISHI LSIs**

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

10 11 12 13 14 15 16 17 0 1 2 3 Δ 5 6 7 8 9 CLK /CS tRC **/RAS** tRCD /CAS /WE CKE DQM XxX A0-8 XxX A10  $X \times X$ A9,11 XoX XoX **BA0,1** DQ Auto-Refresh ACT#0 WRITE#0 After tRC from Auto-Refresh, Before Auto-Refresh, all banks must be idle state. all banks are idle state.

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

## DQM Read Mask @BL=4 CL=3

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

**Preliminary Spec.** Some contents are subject to change without notice.

#### **MITSUBISHI LSIs**

MH16S72APHB -6,-7,-8

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

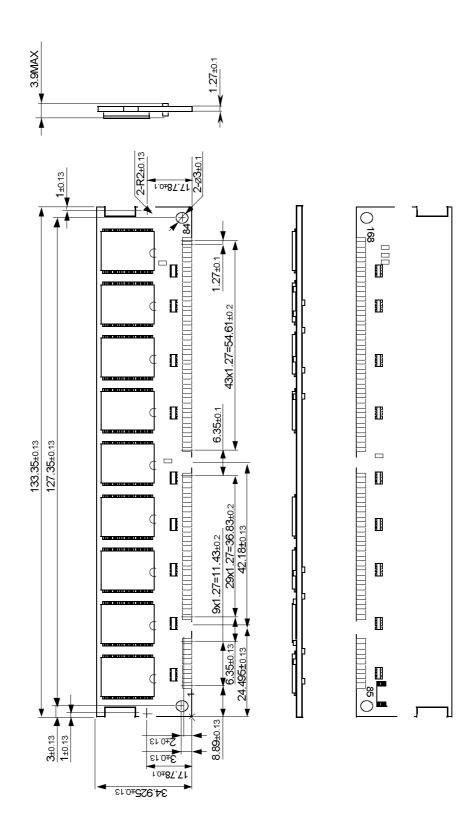

## OUTLINE

1,207,959,552-BIT (16,777,216 - WORD BY 72-BIT)Synchronous DRAM

## Keep safety first in your circuit designs!

Mitsubishi Electric Corporation puts the maximum effort into making semiconductor products better and more reliable, but there is always the possibility that trouble may occur with them. Trouble with semiconductors may lead to personal injury, fire or property damage. Remember to give due consideration to safety when making your circuit designs, with appropriate measures such as (i) placement of substitutive, auxiliary circuits, (ii) use of non-flammable material or (iii) prevention against any malfunction or mishap.

## Notes regarding these materials

1. These materials are intended as a reference to assist our customers in the selection of the Mitsubishi semiconductor product best suited to the customer's application; they do not convey any license under any intellectual property rights, or any other rights, belonging to Mitsubishi Electric Corporation or a third party.